113年9月27日至11月19日Synopsys ASIP Designer Contest

Synopsys(新思科技)聯合台灣半導體研究中心

活動背景:

新思科技的ASIP Designer 不僅是強大的處理器設計工具,更可幫助使用者於當前的 AI 熱潮中脫穎而出!不論你是針對設計 AI 加速的處理器感興趣,或是想瞭解如何優化深度學習和機器學習算法

活動名稱:Synopsys ASIP Designer Contest

主辦單位:Synopsys

協辦單位:台灣半導體研究中心(TSRI)、教育部RISC-V

競賽主題:

Creating extended instructions on the RISC-V CPU through ASIP Designer to accelerate AI models of the MLPerf TinyML benchmark.

參賽資格:

競賽開放國內大專校院電機、電子、

報名方式:

- 參賽者應組隊報名參加比賽,團隊應由至少 1 名學生、至多 3 名學生組成。

- 請由隊長代表所有員報名,請至「2024 Synopsys ASIP Designer Contest」網站報名(https://contest.

synopsys.com.tw/2024ASIP)。

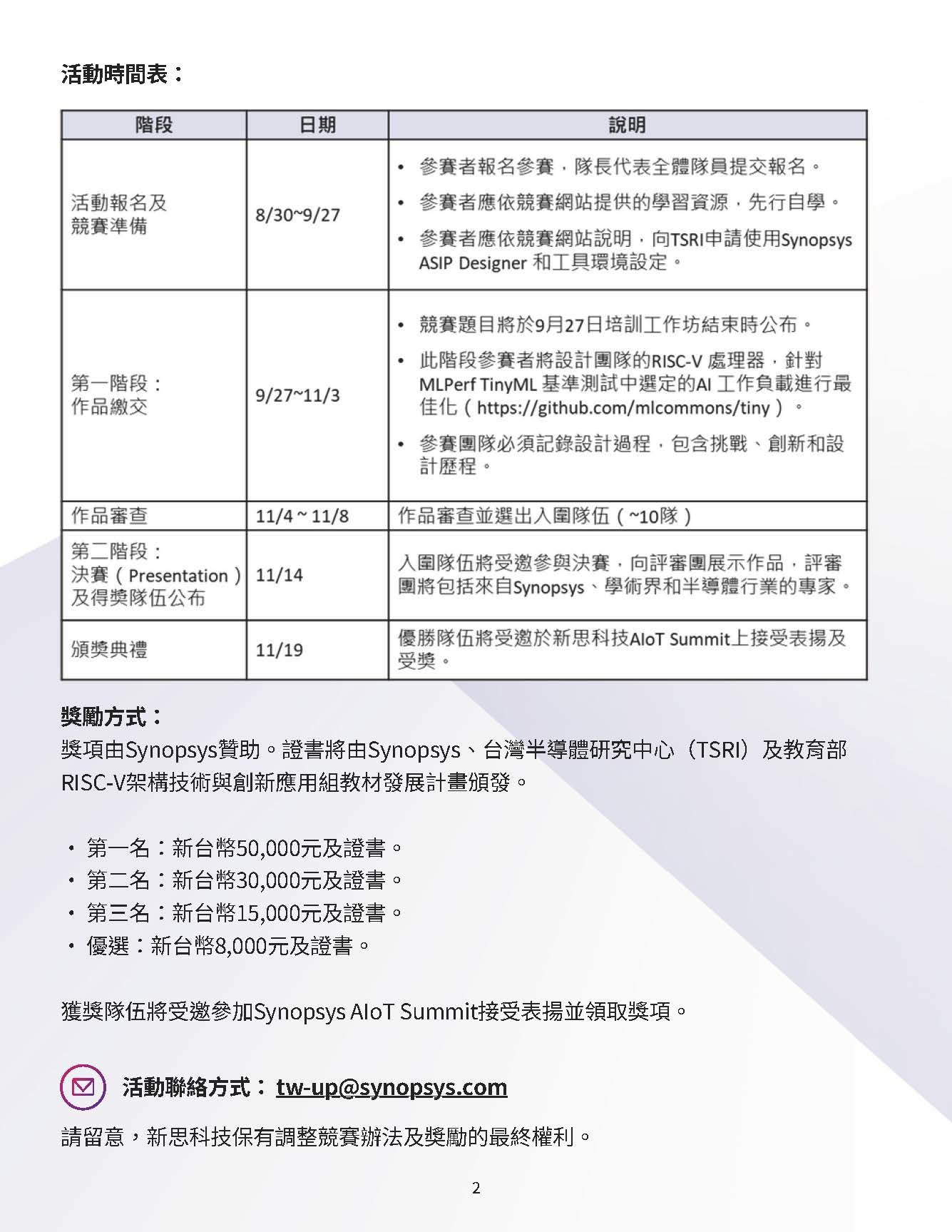

活動時間表:

|

Phase |

Date |

Description |

|

活動報名及 |

8/30~9/27 |

|

|

第一階段: |

9/27~11/3 |

|

|

作品審查 |

11/4 ~ 11/8 |

作品審查並選出入圍隊伍(~10隊) |

|

第二階段: |

11/14 |

入圍隊伍將受邀參與決賽,向評審團展示作品,評審團將包括來自S |

|

頒奬典禮 |

11/19 |

優勝隊伍將受邀於新思科技AIoT Summit上接受表揚及受奬。 |

獎勵方式:

獎項由Synopsys贊助。證書將由Synopsys、

·第一名:新台幣50,000元及證書。

·第二名:新台幣30,000元及證書。

·第三名:新台幣15,000元及證書。

·優選:新台幣8,000元及證書。

獲獎隊伍將受邀參加Synopsys AIoT Summit接受表揚並領取獎項。

活動聯絡方式:

tw-up@synopsys.com